M100PFS - PolarFire RISC-V SoC-FPGA Module

First Industry SoC-FPGA Solution based on Multicore RISC-V Architecture

The M100PFS is based on the PolarFire SoC FPGA architecture by Microchip and combines high-performance 64-bit RISC-V cores with outstanding FPGA technology. The platform integrates a hardened real-time, Linux capable, RISC-V-based MPU subsystem on the mid-range PolarFire FPGA family, bringing low power consumption, thermal efficiency and defence grade security to embedded systems.

The RISC-V CPU micro-architecture implementation is a simple 5 stage, single issue, in-order pipeline that doesn’t suffer from the Meltdown and Spectre exploits found in common out-of-order machines. All five CPU cores are coherent with the memory subsystem allowing a versatile mix of deterministic real time systems and Linux in a single multi-core CPU cluster.

Contact the ARIES Embedded Team to discuss your special requirements on a PolarFire SoC design and how we can help you to achieve optimal results.

Features

- Microsemi PolarFire SoC FPGA

- MPFS025T

23KLE, 68 math blocks, 4x SERDES 12.5Gbit/s, 2x PCIe root port/end point - MPFS095T, available on request

93KLE, 292 math blocks, 4x SERDES 12.5Gbit/s, 2x PCIe root port/end point - MPFS160T, available on request

161KLE, 498 math blocks, 4x SERDES 12.5Gbit/s, 2x PCIe root port/end point - MPFS250T

254KLE, 784 math blocks, 4x SERDES 12.5Gbit/s, 2x PCIe root port/end point

- MPFS025T

- Quad 64-bit RV64GC cores, 667 MHz

- 64-bit RV64IMAC monitor core, 667 MHz

- Processor I/O

- 2x Gigabit Ethernet

- 1x USB 2.0 OTG

- 1x MMC 5.1 SD/SDIO

- 2x CAN 2.0 A and B

- Execute in place Quad SPI flash controller

- 5x multi-mode UARTs

- 2x SPI, 2 I2C

- RTC, GPIO

- 5x watchdog timers

- timers

- Processor to FPGA Interconnect

- 2 64-bit AXI4 processor-to-fabric interfaces

- 3 64-bit AXI4 fabric-to-processor interfaces

- 1 32-bit APB processor-to-fabric interface

- 1 to 8 GByte DDR4 RAM dedicated to the HMS

- 512MByte to 4 GByte DDR4 RAM dedicated to the FPGA

- 128 Mbit to 1GBit NOR Flash

- 8 - 64 GByte eMMC memory

- Clock distribution

- default configuration:

- Gigabit Ethernet

- UART

- CAN

- SPI

- I²C

- USB

- single 3,3V supply

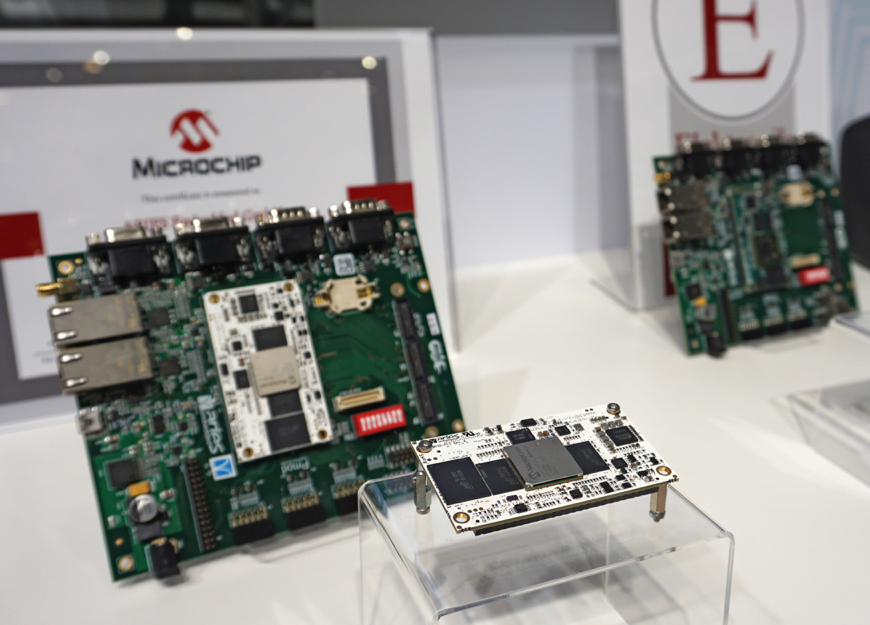

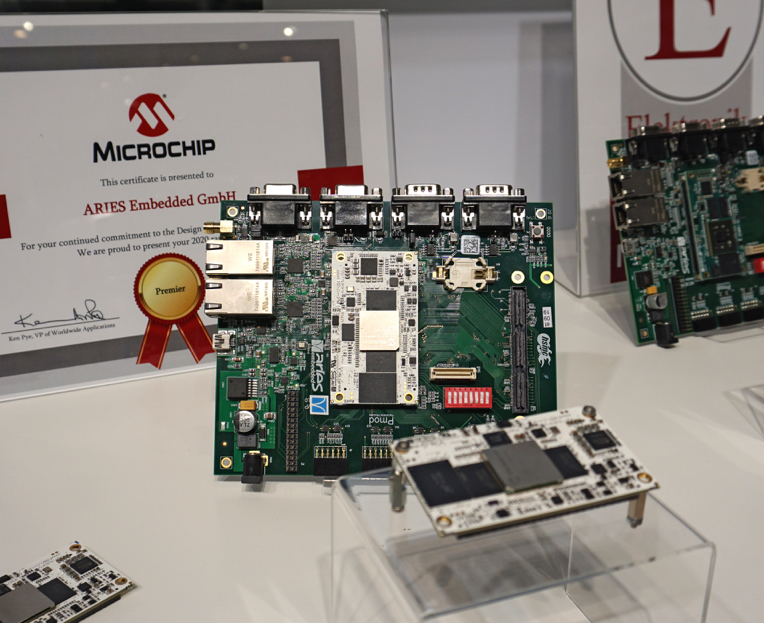

- size 74mmx42mm

- 2 x Samtec QSH-090-01-F-D-A board-to-board interconnect

Block Diagram

Pictures

Order Codes

M100PFS-250BAAB

- MPFS250T PolarFire SoC FPGA

- 254 KLEs

- 784 Math Blocks (18x18 MACC)

- 16x 12.5 Gbps SERDES lanes

- 2x PCIe Gen2 end points/root points

- Total User I/O: MSS-IO / HSIO / GPIO / XCVRs: 136 / 60 / 48 / 4

- 2GB DDR4 SDRAM dedicated to the HMS

- 512MB DDR4 SDRAM dedicated to the FPGA

- 32 MBit SPI NOR Flash

- 4GByte eMMC

- size 74mm x 42mm

- 2 x Samtec QSH-090-01-F-D-A board-to-board interconnect

- 0°C...+70°C

M100PFS System on Modules offer

Low-Power

- Low device static power

- Low inrush current

- Low-power transceivers

Reliability

- FPGA configuration cells single-event upset (SEU) immune

- Built-in SECDED and memory interleaving on FPGA fabric LSRAMs

- SECDED on all processor memories

- System controller suspend mode for safety-critical designs

Security

- Cryptography Research Incorporated (CRI)-patented differential power analysis (DPA) bitstream protection

- Integrated dual physically unclonable function (PUF)

- 56 KB of secure, non-volatile memory (sNVM)

- Built-in tamper detectors and countermeasures

- Digest integrity check for FPGA, μPROM, sNVM, and eNVM

Target Markets

M100PFS SoMs are endorsed for various target markets as

Smart Embedded Vision

- Delivering 4K video and smart imaging

- Applying AI/ML

- Applying imaging to portable products

- Extending battery life

- Eliminating thermal fans and heatsinks

- Achieving secure surveillance

Industrial Automation

- Expanding factory automation networks

- Growing number of M2M sensors and nodes

- Securing decentralized computing

- Improving portability

- Achieving cyber security

- Improving functional safety

Communications

- Significantly improving network capacity and coverage with limited spectrum and CAPEX

- Growing IoT with minimal energy consumption

- Lowering physical and carbon footprint

Internet of Things

- Ensuring lowest power, most secure, edge and gateway devices

- Enabling data processing at the edge, distributed networking systems

- Increasing IoT automation and networking

- Delivering maximum performance with lowest carbon footprint