MSMP1EVK - STMP1 Evaluation Kit

Easy Start and Integration of the MSMP1 SiP

The MSMP1EVK supports a quick start-up of CPU projects and can easily be used as a fast-prototype platform.

The MSMP1EVK contains the Open Standard Module compliant System-In-Package based on ST Microelectronics STMP1 Family architecture offering high-performance single/dual CortexA7 cores in combination with a CortexM4 core. The MSMP1 combines compact design and a wide range of services, bringing low power consumption, thermal efficiency and low-cost to embedded systems.

Features

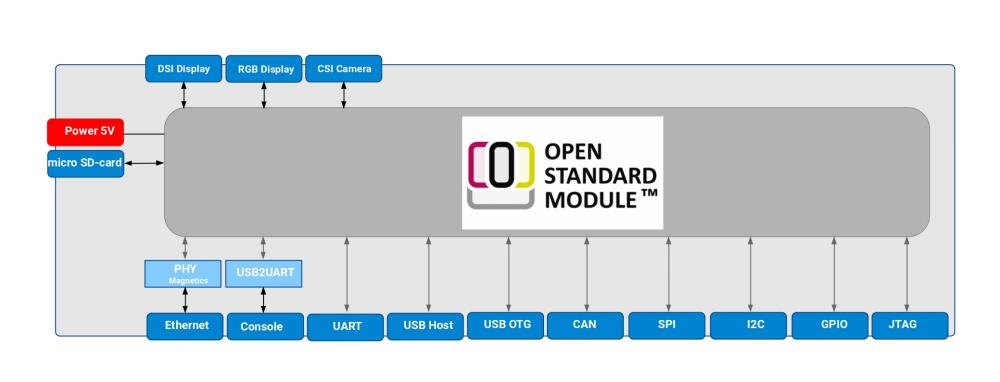

- MSMP1 System on Module

- Ethernet on RJ45 connector

- USB Host on USB A connector

- USB OTG interface on USB microAB connector

- display on FPC connector or pin header

- console interface on USB microAB connector

- UART on pin header

- CAN on pin header

- SPI on pin header

- I2C on pin header

- GPIO on pin header

- JTAG on pin header

Block Diagram

Pictures

Order Codes

MSMP157EVK-BAA

- MSMP1 SiP

- STM32MP157

- 1GByte DDR3L RAM

- 4GB eMMC

- -25...+85°C

- Ethernet on RJ45 connector

- USB Host on USB A connector

- USB OTG interface on USB microAB connector

- display on FPC connector or pin header

- console interface on USB microAB connector

- UART on pin header

- CAN on pin header

- SPI on pin header

- I2C on pin header

- GPIO on pin header

- JTAG on pin header

The idea of all Open Standard Modules is to create a new, future proof and versatile standard for small-size, low-cost embedded computer modules, combining the following key characteristics:

- Completely machine processible during soldering, assembly and testing

- different possible packages for direct PCB soldering without connector

- Pre-defined soft- and hardware interfaces

- Open-Source in soft- and hardware

The Open Standard Module specification allows developing, producing and distributing embedded modules for the most popular MCU32, ARM and RSICV architectures. For a growing number of IoT applications this standard helps to combine the advantages of modular embedded computing with increasing requirements regarding costs, space and interfaces.